von Dr. Wolfgang Rother

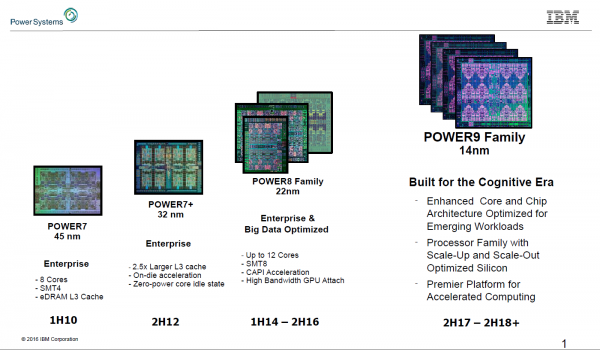

POWER Processor Technology Roadmap

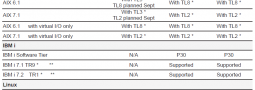

IBM beabsichtigt, die in 2017 vorgestellte Roadmap mit POWER9-Modellen (OpenPower, Linux) noch in diesem Jahr einzuhalten. Die Modelle für die IBM Betriebsysteme AIX und IBM i sollen in 2018 folgen. IBM hat bisher bereits einige Informationen über die POWER9 Architektur veröffentlicht.

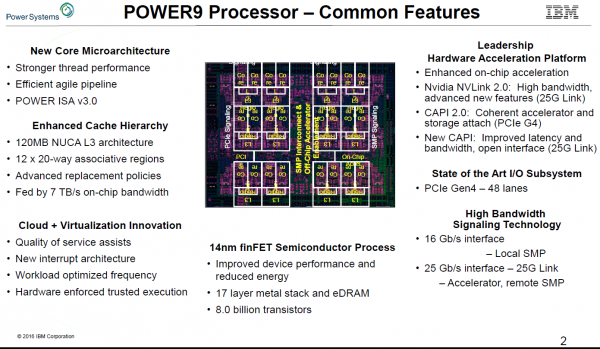

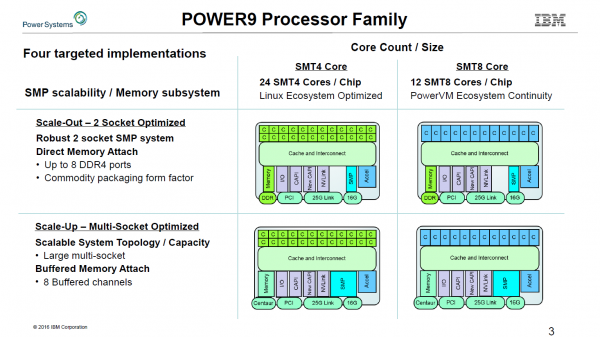

Auf den erstem Blick erkennt man im unteren Bild 24 Kerne, wobei sich jeweils 2 Cores einen L2-Cache teilen. Die I/O-Bandbreite von 7 TB on-chip ist für die Verarbeitung großer Datenmengen ausgelegt, was sich auch in der Verwendung von PCI Gen4 als Busarchitektur widerspiegelt. Ein 16-Gb/s-Link dient für Verbindungen zwischen Sockeln und ein 25-Gb/s-Link für die Anbindung von Akzeleratoren über NVLink2.0, CAPI und OpenCAPI.

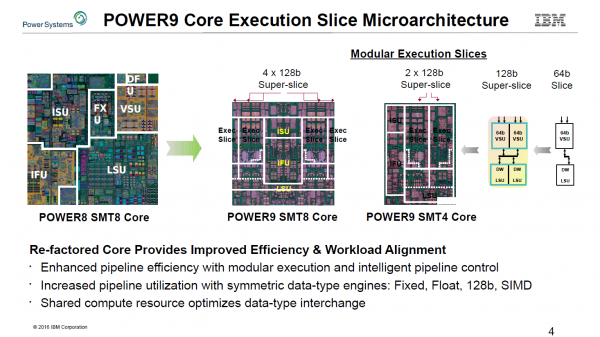

Neben der Prozessor-Architektur gibt es auch Änderungen im Systemdesign. Anhand der POWER9-Architektur können jeweils 2 Kerne zu einem Super-Core zusammengefasst werden.

Damit verringert sich zwar die maximale Anzahl der Kerne von 24 auf 12, aber jeder mit einem dedizierten L2 Cache. Gleichzeitig, da nun mehr Ressourcen zur Verfügung stehen, können statt 4, nun bis zu 8 Threads gleichzeitig von einem Kern in Bearbeitung genommen werden. Diese Prozessoren sind daher für kommerzielle Workload, wie Datenbanken, vorgesehen.

Desweiteren beabsichtigt IBM neben den in POWER8-Systemen üblichen Buffered-DIMMs künftig auch Standard-DDR4-DIMMS in Ein- und Zwei-Sockel-Servern zu unterstützen. Damit ergeben sich vier unterschiedliche Kombinationen.

Vorgesehen sind die 24-Kerner mit den Standard-DDR4-Memory-DIMMs für den Einsatz im Linux- Ökosystem, sprich OpenPower. Zusammen mit der hohen Bandbreite sind solche Maschinen insbesondere für die Bereiche Analytik, Künstliche Intelligenz, Cognitive- und High-Performance-Computing prädestiniert. Dass diese Kerne nur SMT4 unterstützen, ist kein Problem, da hier nur Linux als Betriebsystem vorgesehen ist.

SMT8 dagegen kann von PowerVM-basierten Systemen mit AIX, IBM i und Linux mit bis zu 12 Super-Cores verwendet werden. Es ist in dieser Klasse denkbar, dass der Verzicht auf die teureren Buffered-DIMMs sich im Hauptspeicherpreis bei IBM Scale-Out-Systemen niederschlagen kann.

Für IBM Enterprise-Systeme sind Super-Cores mit Buffered-DIMMs vorgesehen.

Generell bleibt es bei 8 DIMMs pro Sockel, so dass die maximalen Hauptspeichergrößen je nach DIMM- Größe sich verdoppeln oder vervierfachen können.

Wer Planungsinformationen benötigt, kann sich an die IBM oder einen IBM Business Partner wenden. t

Über den Autor

Über den Autor

Dr. Wolfgang Rother arbeitet als Senior IT Specialist Power Systems bei IBM, sein Spezialgebiet ist IBM i. Zu dieser Thematik hat er bereits zahlreiche Fachbeiträge veröffentlicht. Zudem engagiert sich Dr. Rother mit der IBM Academic Initiative dafür, IT-Fachkräftenachwuchs für den Bereich Power Systems zu gewinnen. Dieses Ziel unterstützt er unter anderem mit seiner Tätigkeit als Dozent an verschiedenen Universitäten und Hochschulen.